# 基于模糊综合评价的混合信号芯片测试项优化<sup>\*</sup>

邓可为<sup>1</sup>, 王厚军<sup>1</sup>, 肖寅东<sup>1</sup>, 杨万渝<sup>2</sup>

(1. 电子科技大学自动化学院 成都 611731; 2. 电子科技大学(深圳)高等研究院 深圳 518000)

**摘要:**随着混合信号芯片的复杂性不断提高,芯片测试项数量也大幅增加。然而,快速的芯片生产周期和短暂的产品寿命严格限制了工程师可获得的测试时间。现有测试项优化方法依赖于芯片完整的测试结果,特别是来自缺陷芯片的测试结果。但是在“错误即退出”这种机制下,很难获取缺陷芯片完整的失效表征,使得现有方法与广泛采用的芯片测试机制不兼容。另一种过程能力指标,因为其假定结果呈正态分布,限制了其对非正态分布场景的适用性。针对这些局限性,提出了模糊综合评价法,该方法综合了测试项带来的信息增益、测试结果分布特点、与指标上下限的远近,可适用于更多种类的测试项评估。与以往的方法不同,所提方法仅利用无缺陷芯片数据库进行相关指标参数计算和识别信息量较少、冗余的测试项目,并兼容“错误即退出”机制。该方法在两个不同混合信号芯片的筛选测试和终测过程中进行验证。实验结果表明,增加额外信息增益成本的模糊综合评价法可有效处理非正态分布的测试项,并在保持极低缺陷逃逸率的同时,缩短芯片筛选测试时间66.23%以上,缩短芯片终测时间28.12%。所提方法成果为混合信号芯片测试优化提供了可扩展的高效解决方案,减少了对缺陷芯片特征描述的依赖,提高了大批量芯片制造、筛选过程中的测试效率。

**关键词:**混合信号芯片测试和特征提取;信息获取成本分析;模糊综合评价法;测试项优化;降低测试成本

**中图分类号:** TN47 TN98 TH89      **文献标识码:** A      **国家标准学科分类代码:** 510.30

## Mix-signal chips test optimization based on fuzzy comprehensive evaluation method

Deng Kewei<sup>1</sup>, Wang Houjun<sup>1</sup>, Xiao Yindon<sup>1</sup>, Yang Wanyu<sup>2</sup>

(1. School of Automation Engineering, University of Electronic Science and Technology of China, Chengdu 611731, China;

2. Shenzhen Institute for Advanced Study, University of Electronic Science and Technology of China, Shenzhen 518000, China)

**Abstract:** With the increasing complexity of mixed-signal chips, the number of test items has also grown significantly. However, rapid production cycles and shortened product lifespans impose stringent constraints on the time available for engineers to refine the testing strategies. Existing methods primarily rely on fully characterized results, particularly from failed chips, making them incompatible with stop-on-first-failure mechanism where complete failure characterization is impractical. Another widely used index, the process capability index, assumes normally distributed results, limiting its applicability for non-normal characteristics. To address these limitations, this paper proposes a fuzzy comprehensive evaluation method. It integrates the extra information gain cost (EIGC), the distribution characteristics of test results, and the proximity to upper and lower limits of metrics, making it applicable to a wider range of test item evaluations. Unlike previous methods, our approach solely utilizes the database of passing chips to compute EIGC, enabling the identification and removal of less informative test items without requiring failed chip data, and therefore suitable for stop-on-first-failure mechanism. The methodology has been validated on the binning processes and final test of two different mixed-signal chips. Experimental results show that the fuzzy comprehensive evaluation method with EIGC information can effectively handle non-normally distributed characteristics, and achieves test-time reductions of 66.23% and 28.12%, respectively, in the chip binning process and final test, while maintaining an extremely low defect-escape rate. Our findings provide a scalable and efficient solution for mixed-signal chip test optimization, reducing reliance on failure characterization and improving test efficiency in high-volume manufacturing environments.

**Keywords:** mixed-signal chip test and characterization; extra information gain cost; fuzzy comprehensive evaluation; test set pruning; test cost reduction

## 0 引言

为了确保芯片的可靠性,检测出芯片中的非理想特性和功能、性能缺陷,越来越多测试项被采纳,更全面的芯片测试同时带来了更多的时间和资源消耗,增加了整体测试成本。然而,越来越短的产品上市时间限制了芯片测试的时间。据相关文献报道,缩短使用自动测试设备(automatic test equipment, ATE)测试芯片时间 1 秒/百万个芯片,将可节省高达 60 000 美元成本<sup>[1]</sup>。幸运的是不同测试项之间有很大的相关性,可能覆盖相同芯片故障模型。根据国际商业机器公司(international business machines corporation, IBM)的研究,70%~90% 的测试码无法检测出被测芯片的任何缺陷可被视作为冗余的测试码<sup>[2]</sup>。詹文法等<sup>[3]</sup>也采用 k 均值等算法优化测试向量集来缩短测试时间。

在混合信号芯片测试和特征提取方面也有相类似的现象。由于微小的加工缺陷或工艺变化会导致多个相关参数的性能同时下降,因此往往在相关测试项中有类似的表现,意味着可以在不影响测试质量的前提下删除冗余测试项。因此需要测试工程师对测试项进行评价,在保证故障覆盖率的情况下,最大限度的删减冗余测试项,降低成本。这也逐渐成为半导体测试工程中的一个关键挑战。

目前测试厂商在大规模芯片测试时几乎都采用“错误即退出”的测试机制。在该机制下,一旦测试项结果超出用户设定的阈值范围,直接判断该被测芯片为缺陷芯片,不进行剩余的测试项测试。一方面用户可通过重新安排测试顺序,优先执行失败可能性最大的测试项目来节省时间<sup>[4]</sup>。另一方面,该机制可保护自动测试设备免受意外或不安全测试条件的影响,避免可能在缺陷芯片中遇到的长时间高压引脚短路会对 ATE 硬件造成不可逆的损坏<sup>[5]</sup>。但是,这种策略不会提升无缺陷芯片的测试效率,因为测试过程中未遇到异常,不会触发提前退出的机制。

另外一种测试优化策略旨在尽量减少测试项总数。每个芯片只执行经过筛选后的测试项,而非对被测芯片规格书上列出的所有参数进行测试。相较于对测试项重新排序,此策略同时降低无缺陷芯片和有缺陷芯片的测试成本。但是,被测芯片能通过一个优化过后的测试项子集并不一定意味着其能通过全部测试项。这也因此带来了缺陷芯片被漏检的风险,尤其是在过分追求测试成本最小化的情况下。

支持向量分类算法(C-support vector classification, C-SVC)<sup>[6]</sup>采用线性和非线性高斯核对高维测试空间中

的缺陷区域进行建模和分类划分。在此基础上,加权方案迭代算法被提出用于评价单个测试项目在故障检测中的相对重要性,并移除排名最低的测试项目<sup>[7]</sup>。多目标遗传算法(genetic algorithm, GA)将特征选择和二元分类的框架相结合。该遗传算法旨在通过联合最小化测试成本和预测误差,在原始测试集中寻找遍历一个具有成本效益的子集<sup>[8]</sup>。侯琳杰等<sup>[9]</sup>应用神经网络根据已测量的测试项积分非线性(integral non-linearity, INL)结果预测未测量的信噪比测试项。离散傅立叶变换方法结果也被用于预测芯片动态参数<sup>[10]</sup>,进一步减少了测试项数量。但是以上算法均需用到有缺陷芯片的各个测试项的异常信息用作模型训练,这与“错误即退出”的测试机制相矛盾。在该机制下,每个芯片只可获取最多一个失效测试项的测试结果。

除了以上基于全数据集的测试项评价方法,另一种广泛使用的方法是过程能力指数(process capability index,  $C_{pk}$ )<sup>[11-13]</sup>。 $C_{pk}$ 假设测试结果为正态分布,并量化测量参数分布与该测试项上下限的接近程度。主要优点在于其不需要缺陷芯片的全测试项结果,可只依赖合格芯片的测试数据。但是,并非所有性能参数都遵循正态分布,导致此方法的适用性受到很大限制。

为了解决芯片质量预测中缺乏缺陷芯片全测试项测试结果的问题,之前的工作提出了额外信息增益成本(extra information gain cost, EIGC)指标用于测试项排序<sup>[14]</sup>工作。该方法基于测试项间的相关性,优先测试非相关的测试项。本文进一步根据其表征的每个测试项所贡献的信息增量及其测试资源消耗情况来评估其测试价值。但是该方法仅考虑信息增益,未考虑用户设置的上下边界对测试结果的影响。

本文的主要贡献为:

1) 引入 EIGC 指标用于测试项评价和优化工作。在“错误即退出”的测试机制下,不需要缺陷芯片的完整特性信息的情况下,也能量化每个测试项所贡献的新信息和消耗的测试资源。

2) 结合  $C_{pk}$  指数和正态分布性评判,提出全分布过程能力指数(normalize process capability index,  $NC_{pk}$ ),并采用模糊综合评价法(fuzzy comprehensive evaluation)引入 EIGC 指标,既考虑被测芯片规格参数和测试项之间相关性对测试项优化的影响,又可用于非正态分布数据集,增加算法灵活性和鲁棒性。

3) 在两种类型的混合信号芯片上验证本方法的有效性。实验结果表明芯片在不同温度下的筛选测试和芯片终测均适用所提出的测试项优化评价方法。

## 1 基础理论

### 1.1 芯片测试流程

随着芯片应用的不断扩展,不同使用者在不同使用环境下对相同芯片产生了不同的要求,第三方独立测试机构(如上海伟测)也因此得到蓬勃发展。相较于芯片生产测试可通过扫描链,将测试资源合理有效的分配给各内部功能模块<sup>[15-16]</sup>,在第三方测试中,筛选测试厂商无法获取相关信息,导致无法获得精确的芯片故障模型,应用故障分类算法进行故障诊断<sup>[17]</sup>。

在早期测试阶段,厂商更注重用最少的测试资源进行芯片测试,例如动态设置可接受的工作电流等参数阈值<sup>[18]</sup>,此时一定的缺陷芯片逃逸通常是可以接受的,因为在之后的板级、系统级等测试阶段可以进一步检测未捕获的边缘缺陷类型,最终将总的缺陷芯片逃逸率控制在可接受的低水平<sup>[19-20]</sup>。

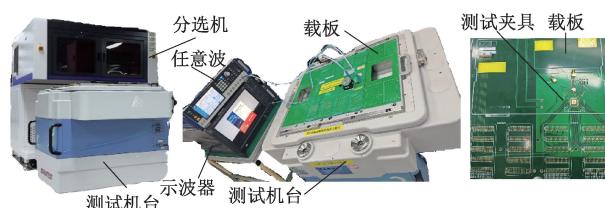

图 1 展示了混合信号芯片实际测试和特征参数提取场景。其中三温分选机(型号 DX2000)将被测芯片从托盘中装载到测试夹具中。它还能提供可靠性测试中的应力条件,例如低温(-55°C)和高温(125°C)。在测试结束后,它也会根据测试结果将芯片移到指定的盒中。ATE 设备(型号 Advantest V93000)用于生成数字测试向量、并检查被测芯片的数字响应。任意波形发生器用于提供锯齿波、正弦波等模拟输入。示波器或频谱分析仪对被测芯片的模拟输出进行采样。插座和载板用于连接被测芯片和测试设备。

图 1 混合信号芯片实际测试场景

Fig. 1 Real test scenario for a mixed-signal chip

### 1.2 过程能力指数

作为一种评估测试项出错概率的方法,  $C_{pk}$  被广泛应用于工业测试中。在数学上,它被定义为测试结果平均值距离最接近上下边界的值并与  $3\sigma$  方差比值,如式(1)所示。

$$C_{pk} = \min \left[ \frac{USL - \mu}{3\sigma}, \frac{\mu - LSL}{3\sigma} \right] \quad (1)$$

其中,  $\sigma$  和  $\mu$  分别代表各测试项目特性分布结果的方差和平均值;  $USL$  和  $LSL$  分别表示被测芯片该规格参数上限和下限。

与其他测试集评价算法不同,  $C_{pk}$  指标不依靠缺陷器件的完整特征数据。相反,其利用已知良好芯片的测试结果分布即可进行缺陷率预测,同时缺陷器件中观察到的首个异常测试项数据也可作为预测的有力补充。此方法优势在于其充分考虑了芯片规格参数对测试结果的影响。 $C_{pk}$  指标本质上基于测试数据为正态分布的假设。然而,根据本文的研究发现,这种假设在实践中并不总是成立的。这导致在非正态分布的情况下,即使设置的  $C_{pk}$  阈值足够高,仍然有超高的缺陷芯片逃逸率。因此,不同的  $C_{pk}$  阈值选取很大程度影响了预测的精度和优化的效率,增加了对专家知识准确性的依赖,降低了测试算法的通用性。

为了更好的应用  $C_{pk}$  指数,本文通过评估测试结果是否符合正态分布(包括数据分布的偏度、峰度和拖尾情况,如式(2)所示),来限制其使用场景,进而减少对非正态分布测试项的优化。

$$\begin{cases} s_{skew} = e^{-\left| \frac{skew(z)}{s_0} \right|^{1.5}} \\ s_{kurt} = e^{-\left| \frac{kurt(z)-3}{k_0} \right|^{1.5}} \\ s_{AD} = e^{-\frac{1}{2} \left[ -n - \frac{1}{n} \sum_{i=1}^n (2i-1) (\ln F(z_{(i)}) + \ln(1-F(z_{(n+1-i)}))) \right]} \end{cases} \quad (2)$$

其中,  $n$  为样本数量,  $z(i)$  为排序后的第  $i$  个样本测试结果;  $F(\cdot)$  为理论分布的累积分布函数;  $skew$  和  $kurt$  定义如式(3)所示。

$$\begin{cases} skew = \frac{\frac{1}{n} \sum_{i=1}^n (x_i - \bar{x})^3}{\left( \frac{1}{n} \sum_{i=1}^n (x_i - \bar{x})^2 \right)^{3/2}} \\ kurt = \frac{\frac{1}{n} \sum_{i=1}^n (x_i - \bar{x})^4}{\left( \frac{1}{n} \sum_{i=1}^n (x_i - \bar{x})^2 \right)^2} \end{cases} \quad (3)$$

以上评价中,三者皆在  $[0, 1]$  范围,越大越“像正态”,故采用几何平均,如式(4)所示,使得每个子分数的不足会被放大,保证“短板效应”。

$$S_N = (S_{skew}^{w_1} S_{kurt}^{w_2} S_{AD}^{w_3})^{1/(w_1+w_2+w_3)}, \quad w_1 + w_2 + w_3 = 1 \quad (4)$$

本文以此提出  $NC_{pk}$  指数,如式(5)所示,当正态分布评价低于阈值时  $NC_{pk}$  衰减至 0,即判定该测试项优化工作不适用于此方法;超过阈值后  $NC_{pk}$  逐步恢复到  $C_{pk}$ ,意味着可用于之后的测试项优化工作。在第 2 章的实测数据验证中,实验结果也表明修改后的  $NC_{pk}$  指数更具备通用性和有效性。

$$NC_{pk} = C_{pk} \cdot \max \left( 0, \frac{S_N - \tau}{1 - \tau} \right) \quad (5)$$

### 1.3 额外信息增益成本

和  $C_{pk}$  指数一样,EIGC 同样仅利用无缺陷被测芯片的测试结果来分析每个测试项目获取的额外信息和相对应

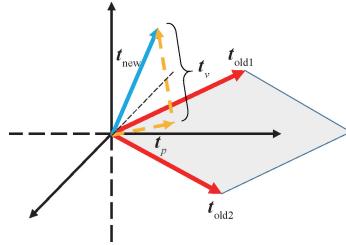

的测试成本开销。其主要思路是采用正交三角分解法得出信息增益。更具体地说是将新测试项目  $t_{\text{new}}$  投影到由之前的测试项  $t_{\text{old1}}$  和  $t_{\text{old2}}$  所创建的超平面上, 如图 2 所示。其中,  $t_v$  代表与新测试项获取的新的被测芯片特征信息, 而  $t_p$  代表可通过先前测试项目中推理得到的先验信息。

图 2 新测试项向量  $t_{\text{new}}$  投影

Fig. 2 Projection of the new vector  $t_{\text{new}}$

为了使得所采集到的数据进一步标准化以及可以更好地进行正交分解, 对每个样本的数据进行去中心化处理。由于测试项数量远高于被测芯片的数量, 所获得的矩阵不为方阵, 无法进行正交分解, 所以本文采用奇异值分解<sup>[21]</sup> (reduced singular value decomposition) 的方法将原始矩阵  $A$  分解为正交矩阵  $U$ 、对角矩阵  $S$  和正交矩阵  $V$  的转置的乘积, 如式(6)和(7)所示。

$$A \in \mathbb{R}^{n \times p}, \quad n \geq p, \quad A = U_{n \times p} S_{p \times p} V_{p \times p}^T \quad (6)$$

$$u_i = [u_{1i} \quad u_{2i} \quad \cdots \quad u_{ni}]^T \quad (7)$$

其中,  $p$  代表测试项目总数。由于其互为正交, 原始数据矩阵可压缩为  $p \times p$  矩阵  $T_0$ , 如式 (8) 所示。

$$T_0 = U_{n \times p}^T A_{n \times p} = S_{p \times p} V_{p \times p}^T \quad (8)$$

为了获取新测试项向量在超平面中的投影分量, 采用吉文斯旋转法通过一系列旋转将给定矩阵  $T_0$  转换为正交矩阵  $Q$ <sup>[22]</sup>。例如, 为了将向量从第  $p^{\text{th}}$  维旋转到第  $(p-1)^{\text{th}}$  维, 需要将吉文斯矩阵  $G_1(p-1, p, \theta_1)$  与  $T_0$  相乘。其中,  $\theta_1$  表示向量旋转的角度。通过适当地选择  $\theta_1, t_{p,1}$  可以变为 0, 同时由于  $G^T G = I_2$ , 所以其为正交矩阵, 这意味着第 1 个测试项目的第  $p$  个维度上的所有信息都被旋转投影到了  $(p-1)$  个维度上, 从而获取了测试项的信息增益。

$$T_i = \begin{bmatrix} t_{1,1}^i & t_{1,2}^i & t_{1,3}^i & \cdots & t_{1,i}^i & t_{1,i+1}^i & \cdots & t_{1,p}^i \\ 0 & t_{2,2}^i & t_{2,3}^i & \cdots & t_{2,i}^i & t_{2,i+1}^i & \cdots & t_{2,p}^i \\ 0 & 0 & t_{3,3}^i & \cdots & t_{3,i}^i & t_{3,i+1}^i & \cdots & t_{3,p}^i \\ \vdots & \vdots & \vdots & \ddots & \vdots & \vdots & \ddots & \vdots \\ 0 & 0 & 0 & \cdots & t_{i,i}^i & t_{i,i+1}^i & \cdots & t_{i,p}^i \\ 0 & 0 & 0 & \cdots & 0 & t_{i+1,i+1}^i & \cdots & t_{i+1,p}^i \\ \vdots & \vdots & \vdots & \ddots & \vdots & \vdots & \ddots & \vdots \\ 0 & 0 & 0 & \cdots & 0 & t_{p,i+1}^i & \cdots & t_{p,p}^i \end{bmatrix}_{p \times p} \quad (9)$$

同理, 第 2 维到第  $p$  维的所有信息都可以通过以下方式旋转到第 1 维。经过不断的吉文斯旋转, 等到上三角矩阵, 如式(9)所示。其中,  $t_{i+1,i+1}$  到  $t_{p,i+1}$  表示新测试项中无法由前  $i$  个测试项表示的分量, 相反,  $t_{1,i+1}$  到  $t_{i,i+1}$  表示已从前  $i$  个测试项获取的信息分量。基于此, 额外信息增益定义为式(10), 即:

$$E(T_i) = \frac{(t_{i+1,i+1}^i)^2 + (t_{i+2,i+1}^i)^2 + \cdots + (t_{p,i+1}^i)^2}{(t_{1,i+1}^i)^2 + (t_{2,i+1}^i)^2 + \cdots + (t_{p,i+1}^i)^2} \quad (10)$$

考虑到每个测试项目所需的测试时间和测试资源消耗各不相同。因此, 为了更好地评价整个测试过程的效率, 额外信息增益成本  $EIGC(T_i)$  被定义为  $E(T_i)/G(T_i)$ , 其中,  $E(T_i)$  指测试项目  $i$  所提供的额外增益,  $G(T_i)$  代表其成本, 包括测试时间和人力资源。总之,  $EIGC(T_i)$  可作为测试项优化的指南, 其中数值最小的测试项目将被删除。

#### 1.4 模糊综合评价法

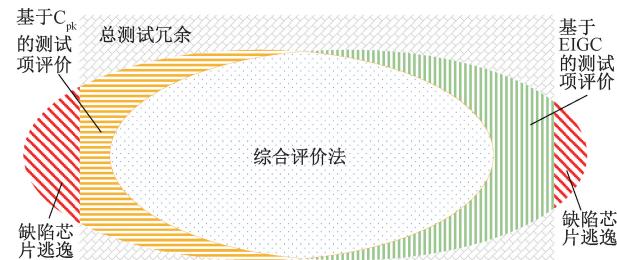

EIGC 测试项评价方法考虑了信息增益成本和测试项之间的相关性, 而  $C_{pk}$  指数则侧重于单个测试项结果的分布特性与其对应的阈值设置。为了充分结合这两种算法的优势, 本研究进一步提出了一种模糊综合评价法。如图 3 所示, 横条和竖条背景块分别代表基于  $C_{pk}$  和基于 EIGC 方法额外发现的冗余。如果  $C_{pk}$  和 EIGC 阈值选择不当或测试项数据不符合假定的正态分布, 则可能出现缺陷芯片逃逸的情况, 由斜条纹表示。2.2 节中的实验也证实了存在此情况。

图 3 模糊综合评价法在测试项优化中对逃逸率的影响

Fig. 3 Impact of the fuzzy-based test set pruning method on defect escape rate

采用模糊综合评价法<sup>[23]</sup>, 与传统的评价方法相比, 该方法可捕捉人类判断中的模糊性和不确定性, 并提供一个综合框架, 将多个阶段的模糊判断结合起来<sup>[24]</sup>, 软判定也降低了对阈值的敏感性和专家先验知识的依赖性。具体实现流程为:

1) 创建因素集, 将影响评价对象的各种因素作为元素所组成的一个普通集合, 表示为  $U = (u_1, u_2)$ , 其中  $u_1$  代表  $NC_{pk}$  评价方式,  $u_2$  代表 EIGC 评价。

2) 建立综合评价的评价集  $V = (v_1, v_2)$ , 其中  $v_1$  代表测试项可优化度,  $v_2$  代表其不可优化度。

3) 各因素  $u_i$  根据需求分配一个权重  $A = (a_1, a_2)$ 。

4) 确定模糊综合评判矩阵  $R_{2 \times 2}$ 。相较于  $C_{pk}$  中硬阈值判定, 此处采用如下所示的 Sigmoid 隶属度函数进行软判定。其中  $a, b$  用来定义过渡区间的两端, 即对应隶属度 99.5%, 并自动换算出中心  $c$  和尺度  $s$ ,  $r_{11}, r_{22}$  对应  $u_1$ ,  $r_{21}, r_{12}$  对应  $u_2$ 。由于本研究中  $V$  仅有两元素, 即可优化或不可优化, 故  $r_{11}$  和  $r_{12}$  互为对称。

$$\begin{cases} r_{11}(x) = \frac{1}{1 + \exp\left(-\frac{x - c}{s}\right)} \\ r_{12}(x) = 1 - r_{11}(x) \end{cases} \quad (11)$$

5) 通过矩阵合成运算  $B = A \circ R$  进行模糊综合评判, 本文采用补偿型幂平均算子。相较于其他算子, 幂平均允许高值对低值一定程度的补偿, 但不会像算术平均甚至“ $OR(x+y-xy)$ ”算子一样容易形成假阳性, 即轻易判定“可优化”。

$$b_k = \left( \frac{r_{1k}^p + r_{2k}^p}{2} \right)^{1/p} \quad (12)$$

本方法引入两个影响因素  $NC_{pk}$  和 EIGC 指数进行模糊综合评价, 得到最终优化后的测试项子集, 并根据此集合完成剩余芯片的测试工作和缺陷诊断。由于芯片不同测试阶段所要求的缺陷芯片逃逸率不同, 此方法同样方便测试人员在不同的测试阶段通过选取不同权重配比和不同隶属度函数, 来获取不同测试项子集, 测试人员也可引入新的评价要素例如资源消耗等, 用于此综合评价法。

## 2 实验验证

本章介绍了对所提出的测试优化算法的实验验证, 并以两款模拟数字转换器 (analog-to-digital converter, ADC) 芯片为例在筛选过程和终测阶段中通过优化冗余测试项达到测试时间的节省。混合信号集成电路的测试数据通常涉及较高的商业机密, 目前没有公开的数据集可用于对比。国内外的相关研究均基于自身采集的一个或两个数据集进行<sup>[4, 9, 19, 25]</sup>。本文中实验使用的被测芯片来自中国电子科技集团公司第二十四研究所, 与其合作进行全参数测试。为了进一步推广到“错误即退出”的测试场景中, 本文的训练阶段仅依赖于无缺陷芯片, 或一类 (bin one) 的良品芯片的测试结果, 避免了对缺陷芯片全面特性分析的依赖。该数据集用于计算 EIGC 和  $C_{pk}$  指标, 并根据模糊综合评价法进行优化。测试项的所有阈值均根据相应的用户手册确定。并且为保证算法验证的公平性, 测试方法遵照电气电子工程师学会

(Institute of Electrical and Electronics Engineers, IEEE) 1241 号标准, 本文并未优化测试方法本身。实际缺陷芯片逃逸率根据式 (13) 计算。其中,  $N_{\text{escape}}$  表示未被经过优化后的测试集检验出的缺陷芯片数量,  $N_{\text{failed}}$  表示真正缺陷芯片的数量。

$$r_{\text{escape}} = \frac{N_{\text{escape}}}{N_{\text{failed}}} \quad (13)$$

### 2.1 ADC 芯片筛选测试

在本节中, 采用一款 250 kSPS、6 通道同步采样、14/16 位 ADC 作为被测芯片开展验证。根据芯片的使用场景要求, 共选择与线性度、噪声表现相关的 30 个动态及静态参数, 作为芯片筛选标准。为了符合航空航天标准 IEC/TS 62564-1, 本文分别在常温 (25°C)、低温 (-55°C) 和高温 (125°C) 条件下进行了芯片筛选测试和算法验证。

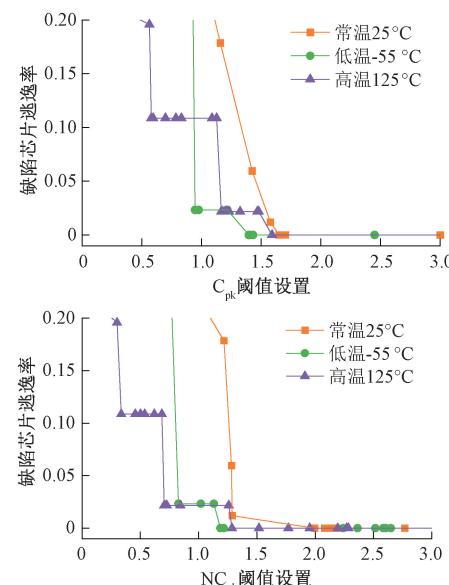

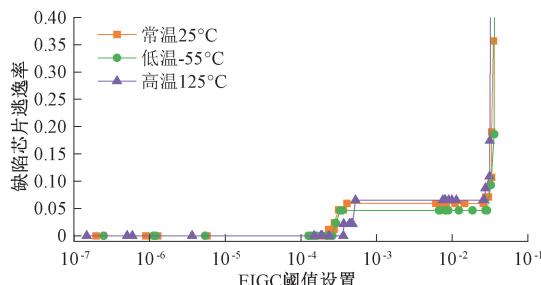

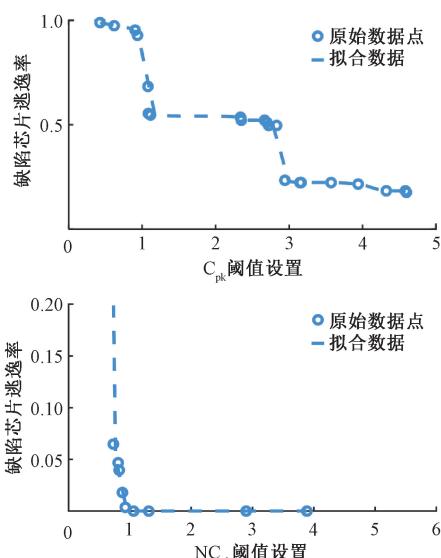

在常温下, 共有 1 012 个被归入 bin one 的芯片, 用于确定各测试项 EIGC 和  $C_{pk}$  值; 84 个失效芯片用于验证所提出的方法的有效性。在高温和低温测试条件下, 分别使用 503 和 506 个芯片用于训练, 46 和 42 个缺陷芯片用于测试。EIGC 和  $C_{pk}$  测试结果分别如图 4、5 所示, 其中方形、圆形和三角形分别表示了常温、低温和高温的测试结果。为了更好的展示测试工程师所关注的缺陷逃逸率细节, 图 4 仅展示  $C_{pk}$  取值在 0~3 部分, 且仅关注缺陷芯片逃逸率 < 0.2 部分。

图 4 不同温度下的缺陷芯片逃逸率与  $C_{pk}$ 、 $NC_{pk}$  阈值的关系

Fig. 4  $r_{\text{escape}}$  versus  $C_{pk}$ ,  $NC_{pk}$  threshold value under different temperature

由于此芯片筛选测试场景仅关注芯片的线性度、噪声系数相关的测试项, 相较于 2.2 节测试场景, 此测试结

图 5 不同温度下的缺陷芯片逃逸率与 EIGC 阈值的关系

Fig. 5  $r_{\text{escape}}$  versus EIGC threshold value under different temperature

果分布更具备正态分布特性,因此图 4 所展示的基于  $C_{\text{pk}}$  和  $NC_{\text{pk}}$  指数的优化结果具备相同的效率。由图 4、5 可见,当阈值被合理设置时,两种测试项评价方法均可以实现在不带来缺陷芯片逃逸的前提下,优化测试项集合。图 5 也验证了 EIGC 算法的有效性,对应 EIGC 值最低的测试项对芯片筛选的贡献最小。

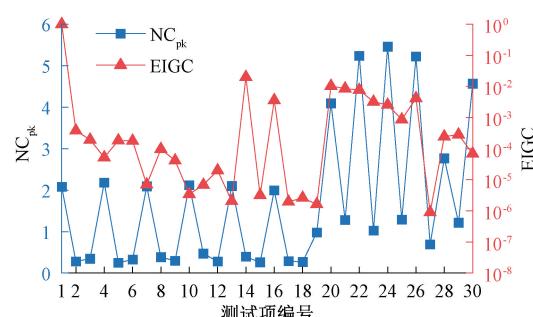

在模糊综合评价法中,  $NC_{\text{pk}}$  对应的逻辑斯蒂隶属度函数(Sigmoid)中  $a$ 、 $b$  分别设置为 0.5 和 2; 在 EIGC 评价中  $a$ 、 $b$  分别设置为  $10^{-6}$  和  $10^{-4}$ 。相较于传统单一参数的评估,本文方法采用了更宽泛的阈值设定范围,具有更广的适应性。图 6 展示了测试项对应的  $NC_{\text{pk}}$ 、EIGC 的评估结果,分别用方形和三角形表示。综合评价集  $v_1$ 、 $v_2$  结果由图 7 所示,  $v_1$ 、 $v_2$  分别使用斜条纹和横条纹作为背景,由于测试项 19、27 的 EIGC 评估结果突出,即其未包含足够多的有效新信息,即使其未能在基于  $NC_{\text{pk}}$  的优化流程中被识别出,在最终的模糊综合评价法中,仍然判定可对其做优化处理,进一步提升测试效率。

图 6 常温下测试项  $NC_{\text{pk}}$ 、EIGC 的评估结果Fig. 6 Evaluation outcome of  $NC_{\text{pk}}$ , EIGC at room temperature

表 1 总结了不同算法下测试时间优化效果以及缺陷芯片逃逸结果,由于基于  $C_{\text{pk}}$ 、 $NC_{\text{pk}}$  和 EIGC 优化结果受阈值有很大影响,所有优化算法都通过提高阈值避免故障芯片逃逸,测试时间提升统一与全参数测试进行比较。

图 7 模糊综合评价法下评价集  $v_1$ 、 $v_2$  结果Fig. 7 Results of  $v_1$  and  $v_2$  outcomes under fuzzy comprehensive evaluation

结果表明  $C_{\text{pk}}$  (阈值 = 1.7) 的优化方法相较于 EIGC (阈值 =  $10^{-5}$ ), 在测试结果呈现正态分布的情况下更有效, 找到 12 项冗余测试项, 大大缩短了测试时间, EIGC 在测试项优化中更保守, 找到 9 项冗余。基于  $NC_{\text{pk}}$  (阈值 = 1.3) 的优化结果和基于  $C_{\text{pk}}$  的保持一致。在模糊综合评价法中, 由于其采用软判定, 并且结合了两种不同的优化方式, 因此总共挑选出了 14 项冗余测试项, 增加测试项 19、27, 测试时间缩短 43.86%。表 1 包含了在常见 3 种高低温下测试结果, 由此可见本文提出的模糊综合评价方法具有通用性。

表 1 不同测试优化算法比较

Table 1 Comparison of different optimization strategies (%)

| 优化算法                | 测试时间提升比例 |       |       | 逃逸率 |      |      |

|---------------------|----------|-------|-------|-----|------|------|

|                     | 25℃      | 125℃  | -55℃  | 25℃ | 125℃ | -55℃ |

| 基于 $C_{\text{pk}}$  | 39.47    | 45.88 | 39.47 | 0   | 0    | 0    |

| 基于 EIGC             | 10.68    | 10.68 | 10.68 | 0   | 0    | 0    |

| 基于 $NC_{\text{pk}}$ | 43.37    | 45.88 | 43.37 | 0   | 0    | 0    |

| 模糊综合评价              | 43.86    | 50.27 | 43.86 | 0   | 0    | 0    |

## 2.2 ADC 芯片终测

在本节中, 芯片终测场景被用来验证所提出的测试项评价、优化方法, 该应用场景也可扩展到其他测试流程, 如晶圆测试阶段。与 2.1 节仅关注器件线性度等性能不同, 本节选择了另一款 16 位 ADC, 包含了芯片测试规范中完整的 24 个测试项。同样在模型训练阶段采用了 590 个被测芯片, 用以计算  $C_{\text{pk}}$ 、 $NC_{\text{pk}}$ 、EIGC 指标。随后, 又测试了 278 个含缺陷的芯片, 用以进行模型验证。

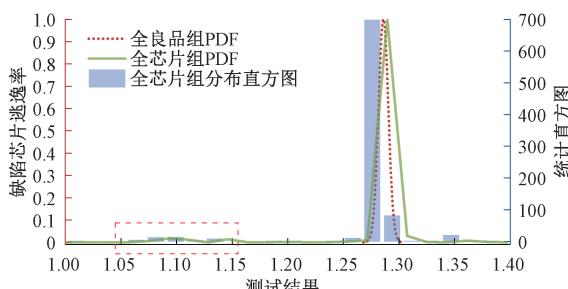

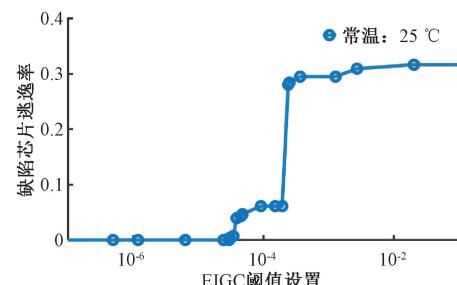

测试项  $V_{CM}$  分布结果如图 8 所示, 其对应的  $C_{pk}$  指数最高, 即该测试项失败的可能性最小。然而在仅基于  $C_{pk}$  的测试项优化算法中, 如果判定该测试项为可优化会导致 49 个缺陷芯片逃逸, 如图 8 中矩形框内测试结果所示。由于非正态分布的测试项存在, 无法通过合适的  $C_{pk}$  阈值设置进行有效的测试项优化, 将缺陷芯片逃逸率控制在可接受的水平, 如图 9 左图所示, 这一实验结果凸显了仅依赖  $C_{pk}$  值进行测试项优化的潜在隐患。而在增加了有关正态分布评价之后, 如图 9 右图所示, 基于  $NC_{pk}$  的测试项优化方法能正确识别出 4 项冗余测试项, 并且针对不满足正态分布的测试项  $V_{CM}$  (测试编号 8)  $S_N$  也大幅降低其  $NC_{pk}$  指数。因此在该方法下可通过设置合理阈值保证了优化后故障芯片的低逃逸率。

图 8 测试项  $V_{CM}$  在全良品数据库和全数据库下数据分布

Fig. 8 Data distributions of test items  $V_{CM}$  in the good-chip-only database and the full-chip database respectively

图 9 常温下的缺陷芯片逃逸率与  $C_{pk}$ 、 $NC_{pk}$  阈值的关系

Fig. 9  $r_{\text{escape}}$  versus  $C_{pk}$ ,  $NC_{pk}$  threshold value

相比之下, EIGC 并不依赖于测试表征结果的正态分布的假设, 而是建立在相关性分析的基础上。如图 10 所示, 当将其阈值同样设置为  $10^{-5}$  时, 缺陷芯片的逃逸率

仍可保持为 0, 同时在 24 个测试项中识别出了 5 个冗余项, 减少了 28.12% 的测试时间, 显示 EIGC 方法具有更大的灵活性和鲁棒性。

图 10 缺陷芯片逃逸率与 EIGC 阈值的关系

Fig. 10  $r_{\text{escape}}$  versus EIGC threshold value

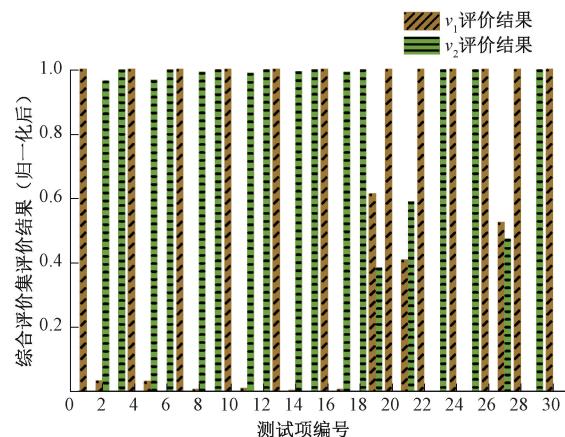

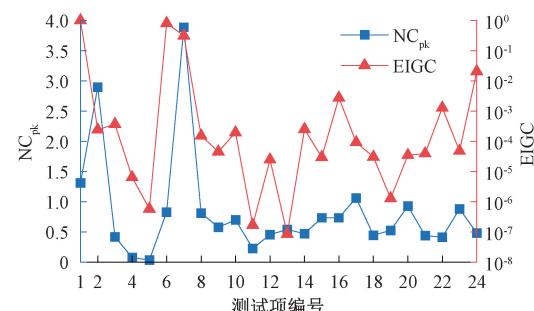

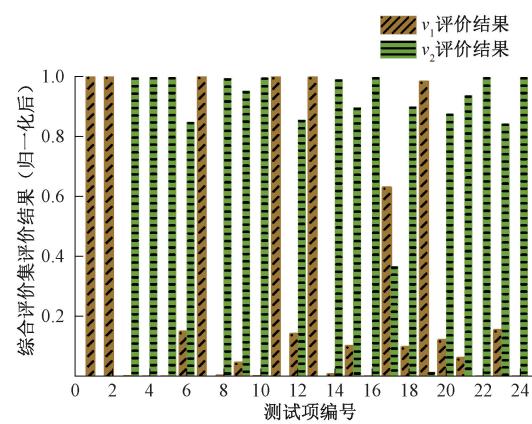

图 11 对比展示了所有测试项对应的  $NC_{pk}$ 、EIGC 的评估结果。模糊综合评价结果如图 12 所示, 本方法进一步综合  $NC_{pk}$  和 EIGC 评估方法, 识别出了更多冗余测试项(测试项 11、13、19), 提升测试项优化效率。并且相较于传统方法需要遵循正态分布的假设前提, 本方法具有更广的适用范围。

图 11 测试项  $NC_{pk}$ 、EIGC 的评估结果

Fig. 11 Evaluation outcome of  $NC_{pk}$ , EIGC at room temperature

图 12 模糊综合评价法下评价集  $v_1$ 、 $v_2$  结果

Fig. 12 Evaluation  $v_1$ ,  $v_2$  outcomes under fuzzy comprehensive evaluation

表 2 总结了芯片在不同测试项优化算法下测试时间减少情况及其对应的缺陷芯片逃逸率。与 2.1 节一样, 若同样将  $C_{pk}$  阈值设置为 1.167, 则会造成 53.6% 的缺陷芯片逃逸, 即使大幅上调阈值至 6, 其缺陷芯片逃逸也高达 17.63%。由于  $NC_{pk}$  指数识别出不符合正态分布假设的测试项, 根据其优化后的测试集依然能保持 0% 的逃逸率。得益于软判定设计, 模糊综合评价进一步优化测试项数量, 减少测试时间 39.37%, 且能保持 0% 逃逸率, 更适用于测试项评估优化工作。

表 2 不同测试优化算法比较

Table 2 Comparison of different optimization strategies

| 优化算法                      | 测试时间/s | 提升比例/% | 逃逸率/% |

|---------------------------|--------|--------|-------|

| 全测试项测试                    | 35.56  | 0      |       |

| 基于 $C_{pk}$ (阈值 = 1.167)  | 10.32  | 70.98  | 53.60 |

| 基于 $C_{pk}$ (阈值 = 6)      | 35.54  | 0.05   | 17.63 |

| 基于 EICC (阈值 = $10^{-5}$ ) | 25.56  | 28.12  | 0     |

| 基于 $NC_{pk}$ (阈值 = 1)     | 31.36  | 11.81  | 0     |

| 模糊综合评价                    | 21.56  | 39.37  | 0     |

### 3 结 论

针对混合信号芯片提出了一种有效的测试项评价方法, 并通过测试项优化提高测试效率。该方法拓展了测试优化算法的使用场景, 无需对缺陷芯片进行完整的特征参数提取, 适用于“错误即退出”的芯片测试场景, 从而解决了现有方法的一个关键局限。相较于传统  $C_{pk}$  指标依赖于测试表征数据结果遵循正态分布的假设, 而所提出的  $NC_{pk}$ 、EICC 指标无需该假设前提, 并且根据此进一步提出了模糊综合评价法, 充分考虑被测芯片参数规格和测试项之间相关性对测试项优化的影响, 结合各自评估方法的优劣。在常见的 3 种可靠性应力条件下, 以两种类型的混合信号芯片为例进行了实验验证。实验结果和理论分析一致, 表明本文提出的模糊综合评价法可实现更高效、更稳健的测试项优化过程。

目前所提出的测试优化方法仅针对被测芯片整体, 并未针对单个被测芯片的提出个性化测试优化方案。因此, 未来的研究会根据被测芯片部分测试结果, 动态优化测试项, 进一步降低测试成本, 并且保证缺陷芯片逃逸率, 提高算法的可靠性和实际应用价值。

### 参考文献

[ 1 ] WANG H F, WU ZH F, LIU W. CNN-based data-model co-design for efficient test-termination prediction [ C ].

- 2022 IEEE European Test Symposium, 2022: 1-6.

- [ 2 ] FERHANI F F, SAXENA N R, MCCLUSKEY E J, et al. How many test patterns are useless? [ C ]. 26th IEEE VLSI Test Symposium, 2008: 23-28.

- [ 3 ] 詹文法, 张鲁萍, 江健生. 基于联合分类的有效测试模式重选方法 [ J ]. 仪器仪表学报, 2023, 44(3): 155-162.

- ZHAN W F, ZHANG L P, JIANG J SH. Effective test pattern reselection method based on joint classification [ J ]. Chinese Journal of Scientific Instrument, 2023, 44(3): 155-162.

- [ 4 ] 肖寅东, 曾宇通, 刘科, 等. 基于 XGBoost 的模拟集成电路测试参数优化方法 [ J ]. 电子测量与仪器学报, 2023, 37(4): 61-68.

- XIAO Y D, ZENG Y T, LIU K, et al. Test parameter optimization method for analog IC testing by XGBoost [ J ]. Journal of Electronic Measurement and Instrumentation, 2023, 37(4): 61-68.

- [ 5 ] STRATIGOPOULOS H G, STREITWIESER C. Adaptive test with test escape estimation for mixed-signal ICs [ J ]. IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems, 2018, 37(10): 2125-2138.

- [ 6 ] SUMIKAWA N, WANG L C, ABADIR M S. An experiment of burn-in time reduction based on parametric test analysis [ C ]. 2012 IEEE International Test Conference, 2012: 1-10.

- [ 7 ] DRMANAC D, LAISNE M, WANG L C. Wafer probe test cost reduction of an RF/A device by automatic testset minimization — a case study [ C ]. 2011 IEEE International Test Conference, 2011: 1-10.

- [ 8 ] STRATIGOPOULOS H G, DRINEAS P, SLAMANI M, et al. RF Specification Test Compaction Using Learning Machines [ J ]. IEEE Transactions on Very Large Scale Integration Systems, 2010, 18(6): 998-1002.

- [ 9 ] 侯琳杰, 解维坤, 陈世博, 等. 一种基于神经网络的 THD 参数快速估计算法 [ J ]. 仪器仪表学报, 2023, 44(2): 101-109.

- HOU L J, XIE W K, CHEN SH B, et al. Fast estimation algorithm of THD based on artificial neural network [ J ]. Chinese Journal of Scientific Instrument, 2023, 44(2): 101-109.

- [ 10 ] DUAN J B, JIN L, CHEN D G. Testing ADC spectral performance without dedicated data acquisition [ J ]. IEEE Transactions on Instrumentation and Measurement, 2012, 61(11): 2941-2952.

- [ 11 ] YILMAZ E, OZEV S, BUTLER K M. Per-device adaptive test for analog/RF circuits using entropy-based process monitoring [ J ]. IEEE Transactions on Very Large

- Scale Integration Systems, 2013, 21(6): 1116-1128.

- [12] BENNER S, BOROFFICE O. Optimal production test times through adaptive test programming [C]. International Test Conference 2001, 2001: 908-915.

- [13] CHEN M J, ORAILOGLU A. Test cost minimization through adaptive test development [C]. 2008 IEEE International Conference on Computer Design, 2008: 234-239.

- [14] DENG K W, WANG H J, PU P, et al. A novel test items evaluation method for mixed-signal system-on-chips based on extra information gain cost [J]. Measurement, 2025, 256: 118160.

- [15] 胡聪, 贾梦怡, 许川佩, 等. 基于时间 Petri 网和 THBA 的 3D NoC 测试规划 [J]. 仪器仪表学报, 2018, 39(1): 234-242.

- HU C, JIA M Y, XU CH P, et al. Research on test planning of 3D NoC based on timed Petri net and THBA [J]. Chinese Journal of Scientific Instrument, 2018, 39(1): 234-242.

- [16] 许川佩, 李克梅. 基于粒子群算法的多约束 3D NoC 协同测试规划 [J]. 仪器仪表学报, 2017, 38(3): 765-772.

- XU CH P, LI K M. Cooperative test scheduling of 3D NoC under multiple constraints based on the particle swarm optimization algorithm [J]. Chinese Journal of Scientific Instrument, 2017, 38(3): 765-772.

- [17] 杨东儒, 魏建文, 林雄威, 等. 基于自注意力机制的深度学习模拟电路故障诊断 [J]. 仪器仪表学报, 2023, 44(3): 128-136.

- YANG D R, WEI J W, LIN X W, et al. A fault diagnosis algorithm for analog circuits based on self-attention mechanism deep learning [J]. Chinese Journal of Scientific Instrument, 2023, 44(3): 128-136.

- [18] 詹文法, 余储贤, 胡心怡, 等. D-PSO 算法的单变量测试参数集成电路筛选方法 [J]. 电子测量与仪器学报, 2024, 38(6): 25-33.

- ZHAN W F, YU CH X, HU X Y, et al. One-variable test parameter integrated circuit screening method for D-PSO algorithm [J]. Journal of Electronic Measurement and Instrumentation, 2024, 38(6): 25-33.

- [19] AHMED I, BARALDI P, ZIO E, et al. A data-driven modelling framework for predicting the quality of semiconductor devices to support burn-in decisions [J]. Computers & Industrial Engineering, 2025, 204: 111115.

- [20] CHO H, KOO W, KIM H. Prediction of highly imbalanced semiconductor chip-level defects in module tests using multimodal fusion and logit adjustment [J]. IEEE Transactions on Semiconductor Manufacturing, 2023, 36(3): 425-433.

- [21] BUNCH J R, NIELSEN C P. Updating the singular value decomposition [J]. Numerische Mathematik, 1978, 31(2): 111-129.

- [22] VENKATESHAN S P. Computational methods in engineering [M]. Boston: Academic Press, 2014: 19-103.

- [23] XU X Y, YU F SH, PEDRYCZ W, et al. Multi-source fuzzy comprehensive evaluation [J]. Applied Soft Computing, 2023, 135: 110042.

- [24] ZHOU R G, CHAN A H S. Using a fuzzy comprehensive evaluation method to determine product usability: A proposed theoretical framework [J]. Work, 2017, 56(1): 9-19.

- [25] CHEN C T, YEN C H, WEN C Y, et al. CNN-based stochastic regression for IDDQ outlier identification [J]. IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems, 2023, 42(11): 4282-4295.

## 作者简介

邓可为, 2018 于电子科技大学获得学士学位, 2020 年于加州大学圣地亚哥获得硕士学位, 现为电子科技大学博士研究生, 主要研究方向是为集成电路测试方法研究, 及测试设备研究。

E-mail: dengkewei@std.uestc.edu.cn

**Kewei Deng** received his B. Sc. degree from University of Electronic Science and Technology of China in 2018, his M. Sc. degree from University of California, San Diego in 2020. He is currently a Ph. D. candidate at University of Electronic Science and Technology of China. His main research interests include integrated circuit test methodology, and test equipment.

杨万渝(通信作者), 2005 于电子科技大学获得学士学位, 2008 年于电子科技大学获得硕士学位, 现为电子科技大学(深圳)高等研究院高级工程师, 主要研究方向为集成电路测试技术。

E-mail: yangwanyu@uestc.edu.cn

**Yang Wan渝** (Corresponding author) received his B. Sc. and M. Sc. degrees both from University of Electronic Science and Technology of China in 2005 and 2008, respectively. He is currently a senior engineer at the Advanced Research Institute of UESTC (Shenzhen). His main research interest includes integrated circuit testing technology.